# CC-Hunter: Uncovering Covert Timing Channels on Shared Processor Hardware

THE GEORGE WASHINGTON UNIVERSITY

WASHINGTON, DC

Jie Chen | Guru Venkataramani | George Washington University | Washington DC, USA

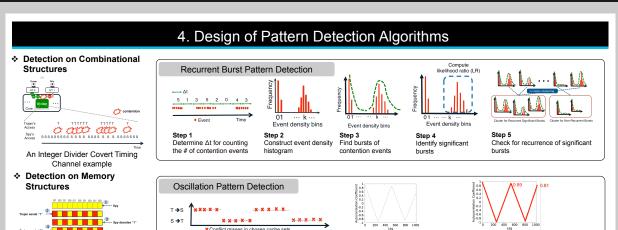

## 1. Problem \* Covert Channels illicitly leaks sensitive secrets to malicious · Trojan (sender) and Spy (receiver) collude to subvert system security policy Covert Timing Channels · Covert Timing Channels are extremely stealthy · Very Challenging to detect and prevent 2. Covert Timing Channel on Hardware Combinational structures · E.g., compute logics and buses Conflict → contention patterns Memory structures with anti-order property and the series E.g., caches Conflict → block replacement 3. How to Detect Covert Timing Channels? **Detection Framework** Identify the event behind conflicts (contention) Construct event train **Apply Pattern Detection Algorithms**

## 5. Hardware Support

Dedicated auditor unit: CC Auditor

A Cache Covert Timing Channel example

Gathers covert timing channel related events Audits two hardware events at any give time

#### Conflict Miss Tracker

Identify conflict miss events, and construct conflict

miss event train for one OS time quantum

Tracks cache conflict miss events

A practical design based on generation bits

Sten 2

Apply autocorrelation to event train.

and construct autocorrelogram

#### ❖ Cache conflicts recorder

Autocorrelogram

Look for oscillation in the

autocorrelogram, that is, autocorrelation coefficients show significant periodicity.

Sten 3

- Two alternating 128-byte vector registers

record the hardware context ID of the

- record the hardware context replacer and victim

## \* Hardware histogram buffer

- 32-bit count-down register for Δt

- 16-bit register for event density in each Δt

- 128-entry histogram

## 6. Software Support

## ❖ Software API

- Places a microarchitectural unit under audit

- OS does privilege checks before letting the user to monitor the unit

## ❖ Software monitor

- Accumulates all data from hardware auditor

- Could be scheduled to run on un-audited cores

## 7. Experimental Setup

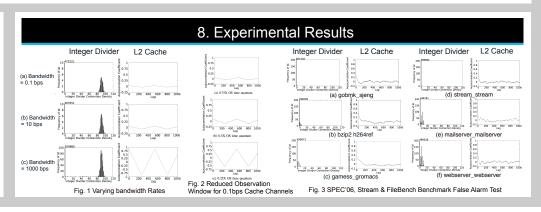

### Cycle accurate full system simulator MARSSx86

- Simulates a Quad core processor, 2.5 GHz, with two hyperthreads

- \* Test on two realistic covert timing channels

- Integer divider and Shared L2 cache

#### \* Evaluation uses combinations of

- · I/O-intensive Filebench server benchmark

- · Memory-intensive Stream benchmarks

- SPEC2006 CPU benchmarks